JMicron SSD Controller Roadmap: JMF680 SATA 6Gbps & JMF815 PCIe Controllers Next Year

by Kristian Vättö on June 12, 2015 3:05 AM EST- Posted in

- Storage

- SSDs

- PCIe SSD

- JMicron

- Computex 2015

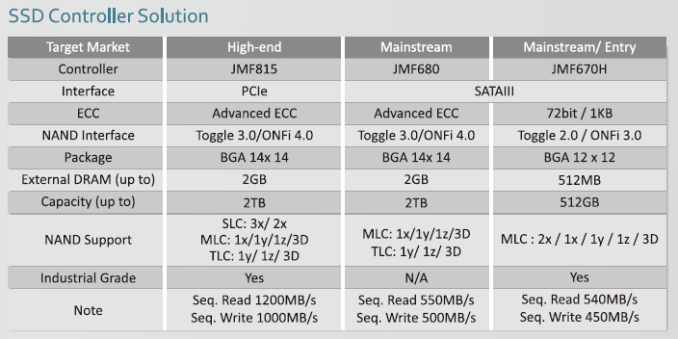

JMicron is getting ready to ship its new JMF670H controller to its customers and we also have reference design samples in for testing, but in its suite at Computex JMicron shed light to its plans for future controllers. We stopped by JMicron last year as well and the plans have since changed a bit.

JMicron is already working on the successor of the JMF670H, which will simply be called JMF680. That's still a SATA 6Gbps design, but it will bring support for TLC NAND thanks to what JMicron calls 'advanced ECC'. JMicron is confident that its ECC implementation will be competitive against the LDPC engines that its competitors have and ultimately I believe that LDPC is more of a marketing gimmick at this point because everyone's ECC algorithms and implementations are slightly different anyway, but the market is associating strong ECC and TLC enablement with LDPC.

Another new feature in the JMF680 is increased capacity support that will go to up to 2TB. That is thanks to the updated (and larger) DRAM controller, which can now support up to 2GB as modern drives typically need about 1MB of DRAM cache per 1GB of NAND. The four NAND channels will also get an upgrade to Toggle 3.0 and ONFi 4.0 standards to support the upcoming NAND dies with faster interfaces. The JMF680 also supports Write Booster, which is JMicron's SLC caching feature that debuts in the JMF670H (more on that in our upcoming JMF670H review).

On the PCIe side JMicron has canceled the JMF810 and JMF811 controllers, and will now be focusing solely on the JMF815. JMicron made the decision to concentrate on the value segment and thus the JMF815 is a PCIe 3.0 x2 design with four NAND channels (no NVMe, unfortunately). A four-lane design would have required moving to 28nm process node, which would have increased the cost substantially and the packaging would have to move away from BGA to FCBGA (used by e.g. Phison and SandForce in their upcoming PCIe controllers) that would further increase the cost. I think it's a good play from JMicron to focus on a segment that isn't as populated because right now everyone is focusing solely on performance with PCIe, but ultimately cost and power consumption will be a major factors in widespread adoption and JMicron should have an advantage there if the JMF815 is executed well.

First engineering samples of the JMF680 and JMF815 are expected to be ready in Q4'15 with first retail products entering the market in early 2016.

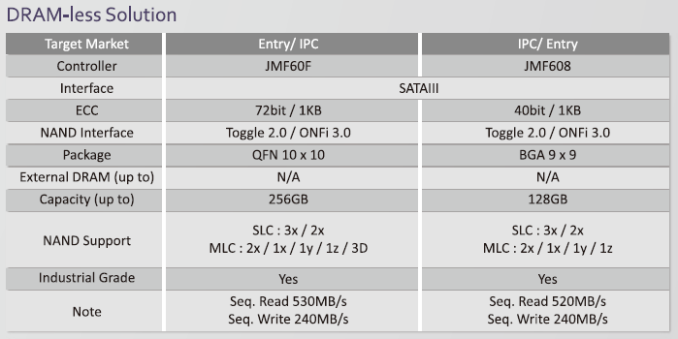

One of the trends I saw at Computex was the move towards DRAM-less SSD controllers. The JMF608 has been relatively popular in China given its ultra-low cost and its successor, the JMF60F, will be available within the next few months. It features an improved ECC engine and a larger capacity support as well as a new, cheaper QFN packaging. Following this trend, I wouldn't be surprised if JMicron also has plans for DRAM-less versions of the JMF680 and JMF815.

All in all, JMicron has a pretty solid roadmap for 2016. It's not aiming to be the performance leader, but to offer cost efficient designs for the value segment. We will have to wait and see how JMicron executes its PCIe controller, but in the meantime stay tuned for our JMF670H review that will be up in the coming weeks!

14 Comments

View All Comments

iwod - Friday, June 12, 2015 - link

What sort of performance lost are we expecting from DRAM-less? We should get much lower power usage ( The DRAM would draw at least 1W? when active ).HexiumVII - Friday, June 12, 2015 - link

Hmmm, i'm wondering if jmicron and sandforce can claw their way back after all their bad former chips. Jmicron with their insanely slow controllers and sandforce with panic mode.Samus - Friday, June 12, 2015 - link

Man, I'm right there with you. I still shudder when I see Jmicron controller BIOS's come up because of their nature to, you know, make RAID arrays disappear and eSATA drives not to detect.Oxford Guy - Saturday, June 13, 2015 - link

The Sandforce panic nonsense was way out of control with the first generation controller at least (e.g. Vertex 2). The second generation couldn't do TRIM properly because of the compression scheme, no matter how many firmware patches were released.Pessimism - Monday, June 15, 2015 - link

Indeed. JMicron provokes my gag reflex.nightbringer57 - Friday, June 12, 2015 - link

Well it could be kind of fine-ish if they learned from the JMF602's inexistant cache....MrSpadge - Friday, June 12, 2015 - link

No, this "1W per chip" figure only applies to the high end and/or high capacity chips of each generation. The DRAM used here can be operated at moderate speed in an energy efficient regime, so I'd expect less power savings than that.bug77 - Friday, June 12, 2015 - link

It's going to be a slow year. We need intel's new chipsets and mobos which will come with more M2 and PCIe slots. Till then, everything is pretty much bottlenecked by the SATAIII interface.Theoretically, there's room for improvement in random operations and mixed usage, but I don't think anyone will be able to figure these out within a year.

SleepyFE - Friday, June 12, 2015 - link

M.2 doesn't work too well in desktop PCs. I am hoping U.2 becomes commonplace soon, or at least sata express.SleepyFE - Friday, June 12, 2015 - link

To clarify: M.2 works, but you need an adapter that takes up your PCIe slot.