The AMD Ryzen 9 7950X3D Review: AMD's Fastest Gaming Processor

by Gavin Bonshor on February 27, 2023 9:00 AM ESTCPU Benchmark Performance: Science

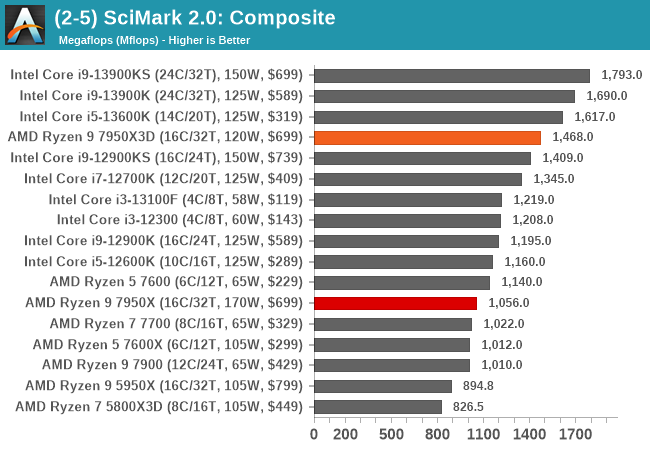

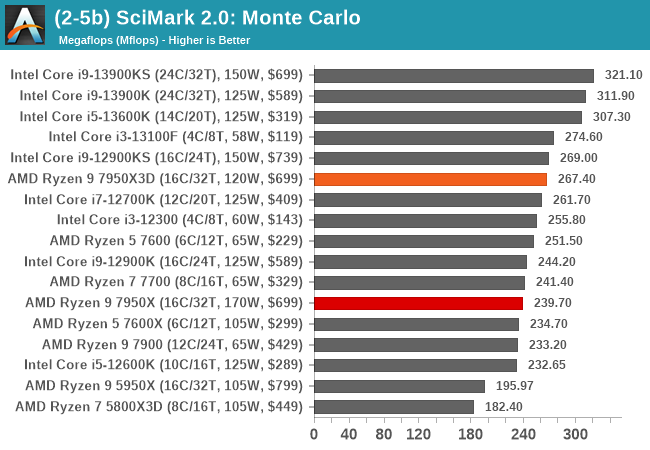

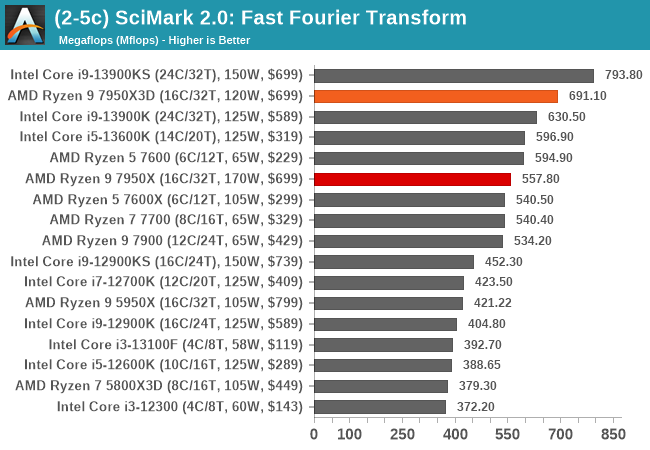

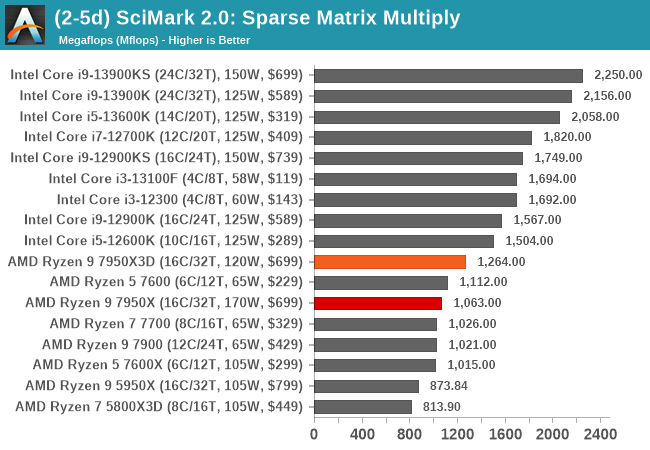

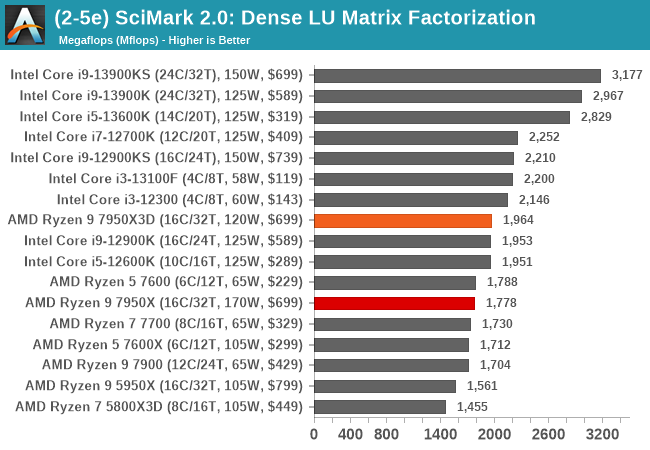

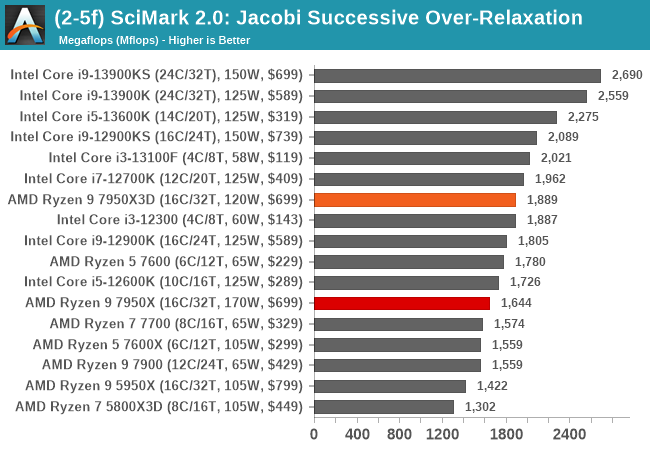

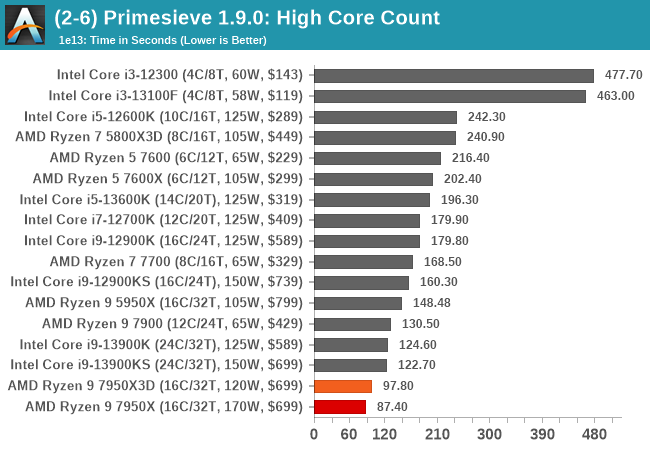

Our Science section covers all the tests that typically resemble more scientific-based workloads and instruction sets. For our 2023 CPU suite, we've also added SciMark 2.0 which measures numerical kernels and various computational routines found in numeric coding.

We are using DDR5 memory on the Ryzen 9 7950X3D and the other Ryzen 7000 series we've tested. This also includes Intel's 13th and 12th Gen processors. We tested the aforementioned platforms with the following settings:

- DDR5-5600B CL46 - Intel 13th Gen

- DDR5-5200 CL44 - Ryzen 7000

- DDR5-4800 (B) CL40 - Intel 12th Gen

All other CPUs such as Ryzen 5000 and 3000 were tested at the relevant JEDEC settings as per the processor's individual memory support with DDR4.

Science

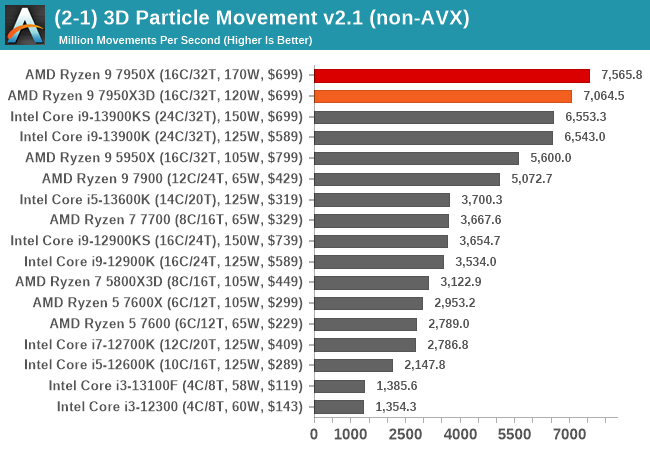

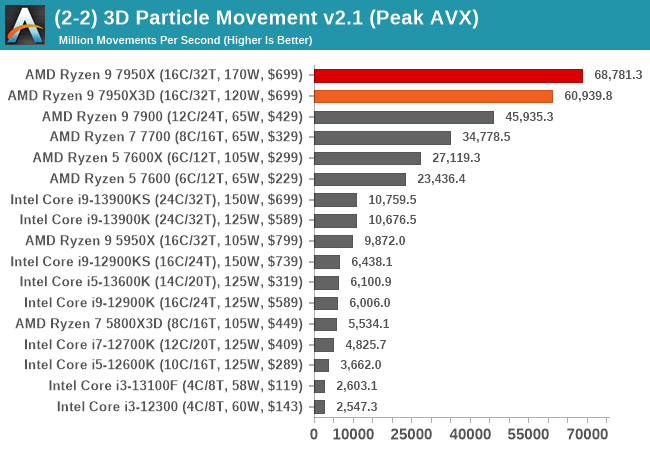

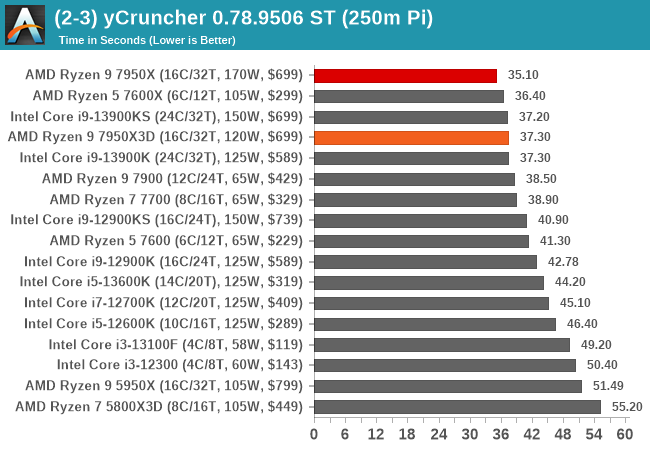

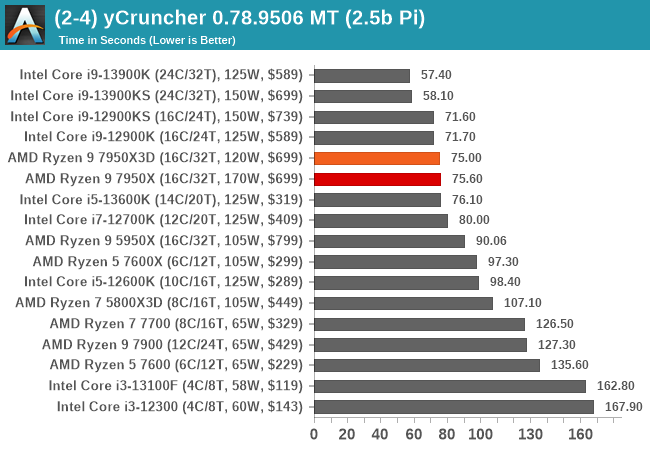

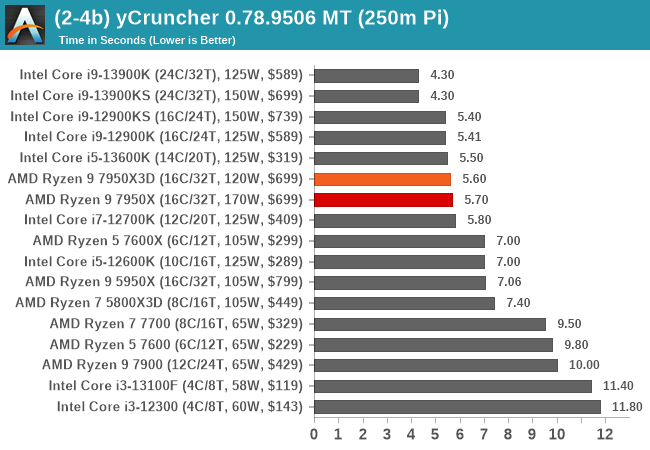

Our science tests focus on scientific-level workloads, and from the above figures, the Ryzen 9 7950X3D performs respectably, as we would expect. The additional 64 MB (128 MB in total across both CCXs) to one of the CCXs does actually provide some benefit in these types of workloads, at least compared directly to the 7950X.

122 Comments

View All Comments

Oxford Guy - Wednesday, March 1, 2023 - link

Has Intel or AMD ever invalidated a warranty for turning on XMP?Please post an article about this to answer that question.

cheshirster - Monday, February 27, 2023 - link

Always has been )They are risking with their "access to the body" by showing AMD on top.

Gastec - Wednesday, March 1, 2023 - link

Well, the world is not feeding trolls as much as it used to do, because of disruptions in the "serials" supply blockchains.HarryVoyager - Monday, February 27, 2023 - link

Definitely looks like AMD is using this as a dry run for their rumored Zen 4c architecture. From the rumors I've seen, they were able to pack about two Zen 4c cores into the space of a standard Zen 4 core by repackaging the logic and removing half the cache. But that means to use them as super E-cores, they need a scheduler that can handle by cache, not frequency like Intel's does.By launching the dual CCD CPUs first, they're able to see and work through those issues now, on a low risk platform before they go full heterogenius. Very shrewd on AMD's part.

nandnandnand - Monday, February 27, 2023 - link

Shrewd, but only if it works in the end. And the buyers of these high-end gaming parts are the beta testers.AvidGamer - Monday, February 27, 2023 - link

That says a lot about the perception and respect AMD has for its ordinary, loyal customers, using them as Beta testers, what a deplorable custom!nandnandnand - Monday, February 27, 2023 - link

It's Alder Lake all over again, but with an apparently dumb method of optimizing for specific programs.We will have to live with it though. big.LITTLE in some form is here to stay over at Intel, and we've seen rumors of Zen 5 + Zen 4C on desktop.

Gastec - Wednesday, March 1, 2023 - link

It's only $700 bucks, come on! Pocket change for successful influencers!AvidGamer - Monday, February 27, 2023 - link

Fully agree with you there! Interesting and thought provoking comment, thanks for sharing your thoughts on this matter! I too believe that some of the practices of AMD are often rather shrewd in their nature...Targon - Tuesday, February 28, 2023 - link

Not even close to what is going on. The 5800X3D was clearly the final chip for socket AM4, and yes, it was primarily focused on gaming since that is where that 3D stacked cache tends to benefit users more.For the Zen4 versions, you will see the 7800X3D, which has one CCD, then the 7900X3D and 7950X3D. For the dual-CCD chips, because GAMES don't use more than eight cores, AMD did the best mix, apply the stacked cache to one CCD, leaving the other CCD without, just so it can be clocked higher. Again, games are pretty much the only chips that show the benefit to the extra cache, so why put the stacked cache on both CCDs?

Zen4c is going to be for servers that will use more cores, but don't need as much cache to operate. When more cores is more important than the very best performance per core, Zen4c makes more sense. There is nothing about stacked cache that applies to Zen4c.

Intel E-cores are pretty much garbage, less functional(they didn't include AVX-512 even when the performance cores did), but more cores DOES benefit certain types of workloads. Note that Intel laptop chips are using this almost to deceive consumers, dual performance core i7s with efficiency cores to make them not as bad will still be worse than any i7 should be. Intel used to sell a lot of low-priced i7 chips with only 2 cores/4 threads, so now, dual-performance cores with some efficiency cores to be not as bad as dual-core i7 chips used to be.

Now, the 7800X3D will be only a single CCD part, so the ONE CCD will have the 3D stacked cache on it. AMD is doing this because the volume of sales for the dual-CCD X3D chips is expected to be fairly low, while the 7800X3D will probably have a very high volume of sales. It's best not to encourage all of the stacked cache modules to go to the 7800X3D where the highest demand will be.