Intel to Revive ‘Tick-Tock’ Model, Unquestioned CPU Leadership Performance in 2024/2025

by Dr. Ian Cutress on March 23, 2021 6:31 PM EST- Posted in

- CPUs

- Intel

- Tick-Tock

- 7nm

- Chiplets

- Pat Gelsinger

- Meteor Lake

- Tiles

As part of today’s announcements, during Intel’s Q&A session after the prepared remarks, CEO Pat Gelsinger explained how Intel is going to revive its fortunes when it comes to its leading edge compute products. One of Gelsinger’s mantras seems to be that unquestioned leadership products bring unquestioned leadership margins for those products, and for Intel to execute, it needs to return to its days of old.

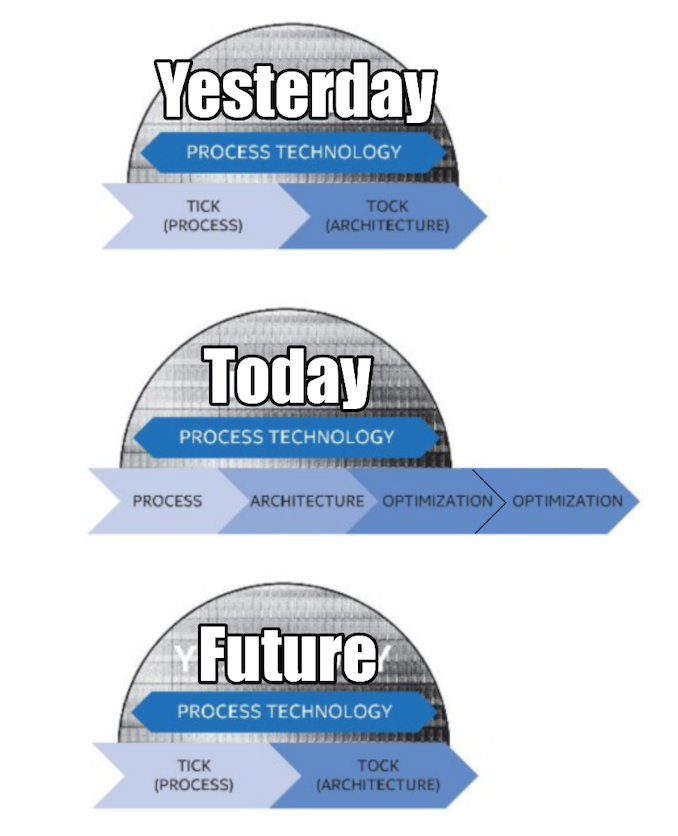

In the past, through the 1990s, 2000s, and into the 2010s, Intel’s manufacturing philosophy was known as ‘Tick-Tock’. This means that for every product generation, the leading edge compute hardware was either a Tick (process node enhancement), or a Tock (microarchitecture enhancement). Each generation would alternate between the two, allowing Intel to take advantage of a familiar design on a new process node, or using a mature node to enable a new performance-focused design. That policy was scuppered when delays to Intel’s 10nm forced Intel into more of a Tick-Tock-Optimization-Optimization-Optimization model.

Today CEO Pat Gelsinger stated that at Intel’s core it has to re-establish the Tick-Tock model that enabled repeated leadership in the CPU ecosystem, buoyed by a healthy CPU roadmap. Part of this is re-establishing discipline in Intel’s ranks to continually provide both microarchitecture updates and process node updates on a regular expected cadence. Pat stated as part of the call that Intel will look towards a confirmed yearly process node improvement, and as a result, there might be a lot of Ticks in the future, with a push to more Tocks as well.

On top of this commentary, Pat Gelsinger also stated that Intel’s CPU roadmaps are already baked in through 2021, 2022, and 2023. The company is thus looking to 2024/2025 for ‘unquestioned CPU leadership performance’, which traditionally means the fastest processor for single thread and multi-thread workloads. This is for sure a laudable goal, however Intel will also have to adapt to a changing landscape of chiplet processor designs (coming in 2023), enhancing on-die accelerators (GNA already present), and also what it means to have leadership performance – in the modern era, leadership performance doesn’t mean much if you’re also pushing lots of Watts. Intel stated that its 7nm process is now comfortably on track to deliver Meteor Lake, a client CPU using tiles/chiplets, in 2023, however we are likely looking to a 7nm variant or even external processes for a 2024/2025 product. Intel has also stated that it is looking to consider the core of its leading edge compute on external foundry processes, although one might argue that this doesn’t explicitly say ‘CPU’.

It is also worth noting that Intel/Gelsinger isn’t calling its disaggregated silicon as ‘chiplets’, and prefers to use the term ‘tiles’. This is because Intel’s tiles amount to long wires across 3D packaging technologies like EMIB and Foveros, compared to package-based multi-die interconnect that require buffers as well as control fabric. Tiles by this definition are more costly to implement than chiplets, and have additional thermal considerations by having high-powered silicon close together, so it will be interesting to see how Intel balances these new packaging technologies with the more cost-sensitive elements of its portfolio, such as client processors.

It’s been known that Intel’s microarchitecture teams haven’t been idle waiting for 10nm to come through the pipe, with a number of designs ready and waiting to go for when the process node technology matures. With any luck, if Intel can get a headwind with 7nm, when 2024 rolls around it might all come thick and fast.

109 Comments

View All Comments

edzieba - Thursday, March 25, 2021 - link

"What would you call the more than 40 pieces in the xe-hpc?"Tiles.

Chiplet = interconnect through substrate, requires TX/RX at either end of link and protocol translation (die <> link <> die). Power per bit high (though lower than through PCB).

Tile = interconnect through silicon, does not require dedicated drivers and may or may not not have specific inter-tile protocol (protocol more for interchangeability when desired, e.g. HBM, otherwise tiles can be treated as if silicon were monolithic). Power per bit low (though higher than monolithic silicon due to TSV resistance).

Spunjji - Friday, March 26, 2021 - link

So far we have two great examples of chiplets on the market (Zen 2 and 3) and one astonishingly mediocre example of stacked dies (Lakefield).EMIB certainly looks promising, but Foveros is not yet something I can bring myself to get enthusiastic about.

watzupken - Wednesday, March 24, 2021 - link

I think Pat said a lot of great things, but talk is cheap. Intel did not voluntarily stop their Tick Tock cycle. They were forced to because their could not deliver 10nm on time. So unless him joining Intel can miraculously overcome all these obstacles, then I will buy his marketing. 2024/25 is really not that far away when you consider the fact that it takes many years to build a quality CPU from scratch. Moreover without their fab advantage, Intel needs to work a lot harder to keep themselves competitive. So looking forward to see if Pat can bring these supposed miracles to turn this oversized “lorry” around in 4 years.JayNor - Wednesday, March 24, 2021 - link

There was some announced plan to simplify the design rules so they could push out the decision on process. Perhaps they discovered this is not so easy, or it is still a work in progress.Otritus - Wednesday, March 24, 2021 - link

One reason why Intel found it hard to shrink their node was the massive increases in density. 14nm was 2.7x as dense as 22nm+, and 10nm was 2.7x as dense as 14nm++. Most foundries go for 1.6x to 2x density improvements per major node shrink. Being less aggressive on the density improvements would allow for Intel to tick more frequently.JayNor - Wednesday, March 24, 2021 - link

Intel is already producing 7nm xe-hpc compute chiplets.Bagheera - Friday, March 26, 2021 - link

Intel has been "producing" 10nm since 2016.there's a thing called *yield*.

Spunjji - Friday, March 26, 2021 - link

Yup. It's no surprise they tried to memory hole Cannon Lake.I'd hate to see how many functional dies they get per wafer on 7nm right now.

willis936 - Wednesday, March 24, 2021 - link

It took the "tick-tick-tick-tock" joke to be at least half the age of the "tick-tock" model for Intel to even acknowledge that tick-tock is currently a dream.The first step to fixing a problem is admitting you have one. I hope to see less bullshit and more competition.

oklukar - Wednesday, March 24, 2021 - link

"One of Gelsinger’s mantras seems to be that unquestioned leadership products bring unquestioned leadership margins for those products, and for Intel to execute, it needs to return to its days of old."So I guess this Gelsinger guy believes that AMD will simply stand still and watch them pass by. 🤦🏽♂️

As the saying goes: you only get one! 😉